Изменение маркировки 7-й серии, UltraScale, UltraScale+ и новых продуктов Xilinx

Компания Xilinx сообщила об изменениях маркировки для устройств седьмой серии, Zynq 7000, Zynq® UltraScale+™, UltraScale™, and UltraScale+™, а также продуктов для коммерческого/промышленного использования (маркировка «XC»), оборонной промышленности (маркировка«XQ») и автомобильных устройств (маркировка «XA»). Изменения не касаются формы, соединительных элементов, функциональности и надежности перечисленных устройств.

В дополнение к внешней маркировке 2D штрих-кодом, компания Xilinx будет упрощать маркировку всех новых устройств, которые входят в серию продуктов Xilinx 7: Zynq-7000, Zynq UltraScale+, UltraScale, UltraScale+, коммерческих/промышленных устройств “XC”, оборонной промышленности “XQ”, а также устройств для автомобильной отрасли «XA» (подробнее см. документы XCN16014 и XCN18016). Лицевая маркировка теперь будет отсутствовать, за исключением логотипа компании (Xilinx), 2D штрих-кода, сведениях о стране-производителе и маркировке семейства (как опции). Это будет способствовать улучшению отслеживания устройств и повышению их безопасности.

Серийный номер продукта можно будет узнать с помощью специального приложения, установленного на мобильном устройстве с камерой, путем сканирования 2D штрих-кода. Данные о продукте и его упаковке теперь могут быть получены только после определения уникального серийного номера и его ввода в специальном мобильном приложении или соответствующей форме на официальном веб-сайте (подробнее см. X CN16014 и XTP424). Чтобы получить полный доступ ко всей информации о продукте нужно отсканировать код LPN, который находится на внутренней стороне упаковки и этикетке изделия.

Продукты, которых коснулись изменения

Изменения касаются всех устройств Xilinx серии 7 Zynq-7000, Zynq UltraScale+, UltraScale, UltraScale+, коммерческих, промышленных XC, автомобильных XA и для оборонной промышленности XQ независимо от комплектации, производительности и температурного класса. Изменения касаются также всех продуктов, созданных по спецификации SCD. Для получения подробной информации об обновлении см. X TP544.

Новые продукты и расширенное семейство устройств Xilinx серий 7, Zynq-7000, Zynq UltraScale+, UltraScale, а также UltraScale+ коммерческого/промышленного назначения «XC», для оборонной промышленности «XQ» и автомобильной отрасли «XA», произведенные 12 июля 2019 года и позже будут отгружаться с новой упрощенной маркировкой. Это изменение касается также инженерных образцов с маркировкой ES и SCD.

Ключевые даты и информация для заказа

Компания Xilinx начнет поставки продуктов и устройств расширенного семейства с новой упрощенной маркировкой на верхней части с 1 июля 2019 года.

Выпускаемые на данный момент продукты получат новый тип маркировки в более поздние сроки. Чтобы узнать точные даты обновления см. X TP544.

Продукты, которых касаются описанные изменения, имеют специальную маркировку на верхней части упаковки, как это показано на Рисунке 1 и Рисунке 2. Новая упрощенная верхняя маркировка включает логотип Xilinx, логотип семейного бренда (опционально), 2D штрих-код и сведения о стране-производителе.

Компания Макро Групп является официальным партнёром Xilinx на территории России.

Сегодняшние системы имеют тенденцию в развитии, когда при уменьшающихся размерах конструкции и схемы предоставляется увеличивающийся функционал при одновременном снижении стоимости. Каждое новое семейство Xilinx FPGA предоставляет увеличение быстродействия и расширенные возможности. Несмотря на то, что система Platform Flash PROM предоставляет простое, заранее созданное решение заливки конфигурации для Xilinx FPGA, другое решение для конфигурирования FPGA, основанное на встроенном микроконтроллере, может улучшить гибкость разработки и уменьшить реальные размеры печатной платы (если предположить, что микроконтроллер располагает достаточным количеством памяти).

Для программирования FPGA микроконтроллером требуется 3 компонента: собственно сам микроконтроллер, какая-то энергонезависимая память (она может быть внутри микроконтроллера или подключена отдельно), и CPLD. Стоимость и размеры конструкции могут быть уменьшены, если функция выделенного устройства конфигурации, такого как PROM, может быть интегрирована в этих трех компонентах. Схема системы показана на рис. 1.

Рис. 1. Диаграмма системы программирования FPGA.

Примечание: иногда CPLD не нужна, если микроконтроллер имеет в наличии достаточное количество выводов GPIO для подключения FPGA. В таких системах Xilinx FPGA может быть сконфигурирована напрямую от микроконтроллера. Для такого типа конфигурирования этот апноут все еще применим. Общая процедура конфигурирования остается прежней, однако пользователь должен изменить исходный код, чтобы микропроцессор управлял выводами GPIO вместо управления шиной адреса и данных.

Вместо использования отдельной PROM, поток бит для конфигурирования может быть взят из незадействованной энергонезависимой памяти системы. Кроме того, микроконтроллер (основная цель которого в выполнении других задач) может также использоваться, чтобы координировать загрузку конфигурационных данных в устройство Xilinx FPGA. Неиспользуемые биты регистров CPLD, доступные для микроконтроллера, могут использоваться для мониторинга и управления битами control, data и status микросхемы FPGA. Когда у микроконтроллера недостаточное количество ножек для управления, простая микросхема CPLD может отобразить часть адресного пространства микроконтроллера для управления конфигурацией FPGA. С использованием этого метода CPLD устанавливает синхронный интерфейс между микроконтроллером и Xilinx FPGA. Такой интерфейс также может предоставить микроконтроллеру выполнить несколько расширенных функций, таких как частичное реконфигурирование или обратное чтение (проверка) конфигурации.

Программирование семейств Virtex и Spartan FPGA с использованием микроконтроллера может происходить либо в режиме Slave Serial, либо в режиме SelectMAP. Между этими режимами есть несколько общих черт. Самое главное в том, что общий поток данных конфигурации идентичен для обоих режимов (см. рис. 2).

Рис. 2. Процедура конфигурирования.

Примечание: некоторые семейства Spartan FPGA задействуют термин параллельного режима конфигурирования (parallel mode). Параллельный режим эквивалентен по функции режиму SelectMAP (режим SelectMap также называют режимом Slave Parallel). См. даташиты Spartan FPGA для получения подробностей. Spartan/XL FPGAs не поддерживают parallel mode.

• Power-Up (включение питания). Это момент первой подачи питания на устройство (микросхему) FPGA. При этом внутренняя машина состояний сбрасывается, и устройство начинает пробуждение. В этот момент оба вывода, и ~PROGRAM, и ~INIT переводятся схемой FPGA в состояние лог. 0.

• Device Initialization (инициализация устройства FPGA). Устройство правильно запитано, но внутренняя конфигурационная память нуждается в сбросе. Этот момент конфигурирования сигнализируется переводом вывода ~PROGRAM в состояние лог. 1 и ~INIT немного позже в лог. 1 (эта задержка указана в даташите на соответствующее устройство FPGA). Устройство FPGA может находиться в этом состоянии сколько угодно долго, если пользователь удерживает снаружи сигнал ~PROGRAM или ~INIT в состоянии лог. 0.

• Configuration Load (загрузка конфигурационных данных). Начало фазы загрузки конфигурации сигнализируется переходом сигнала ~INIT в состояние лог. 1. После этого считываются выводы режима M2:M0 — эти выводы определяют, какой должен использоваться режим загрузки конфигурации. Обратитесь к даташиту на устройство, чтобы определить, как нужно установить эти выводы для требуемого режима загрузки конфигурации. В этой фазе устройство принимает конфигурационные данные. Все события конфигурирования происходят по нарастанию (фронту) тактового сигнала CCLK.

После того, как ~INIT перешел в лог. 1, по каждому фронту перепада сигнала CCLK будет загружен 1 бит конфигурационных данных Slave Serial (этот бит подается на вывод DIN, параметры времени для установки уровня и его удержания см. в соответствующем даташите на устройство FPGA). В таблице 1 показаны выводы, задействованные для режима конфигурирования Slave Serial.

Таблица 1. Описание выводов Slave Serial.

Для режима SelectMAP имеется 2 дополнительных сигнала ~CS и ~WRITE. Оба этих сигнала должны быть выставлены в лог. 0 для того, чтобы байт конфигурации был передан в FPGA. Третий сигнал BUSY является выходом FPGA. Когда конфигурирование SelectMAP работает слишком быстро (например, с частотой больше 50 МГц для семейств Virtex), то сигнал BUSY должен опрашиваться, чтобы гарантировать полную передачу данных. Переход BUSY в лог. 1 показывает, что данные еще не переданы, и должны удерживаться на шине данных.

Примечание: проверьте соответствующий даташит используемого семейства FPGA для наличия вывода BUSY и частоты CCLK, свыше которой вывод BUSY становится активным. Также см. соответствующий даташит для параметров времени установки и удержания всех сигналов. Этот апноут показывает пример дизайна конфигурирования SelectMAP только для 8-битной шины SelectMAP. Некоторые семейства FPGA также поддерживают 16- или 32-битные шины SelectMAP. С подходящими модификациями, учитывающими порядок следования бит данных, показанный здесь пример дизайна может быть расширен для шин данных SelectMAP на 16 или 32 бита. См. руководство пользователя конфигурирования для Вашей целевой FPGA, чтобы определить поддерживаемые разрядности шины и порядок следования бит на шине.

Таблица 2. Описание выводов Slave-SelectMAP.

Поскольку поток бит конфигурации загружается в память, подключенную к микроконтроллеру (или в его внутреннюю память), то этот поток бит должен быть отформатирован в том порядке, в котором его может использовать программа микроконтроллера (независимо от того, как будет программироваться память). Чтобы поддержать разные решения для конфигурирования, инструментарий Xilinx (который входит в состав ISE Design Tools) может сгенерировать данные в различных форматах (см. таблицу 3).

Таблица 3. Xilinx Tool Formats.

Прим. переводчика: если сравнить содержимое файла *.bit и *.bin, то их содержимое полностью совпадает, за исключением первых 77 байт, которые добавлены в файле *.bit как заголовок.

По умолчанию файл *.bin в проекте ISE PlanAhead не генерируется. Чтобы настроить его генерацию, нужно для bitgen указать дополнительную опцию. Для этого зайдите в настройки проекта (Bitstream Settings), раздел Bitstream имеет поле ввода More Options* (дополнительные опции, которые можно добавить вручную). Введите в это поле -g Binary:Yes и нажмите Apply и OK.

С точки зрения порядка следования бит режим конфигурирования Slave Serial очень прост. Загрузка начинается с первого бита из битового потока конфигурации и продолжается бит за битом, пока не будет достигнут конец файла.

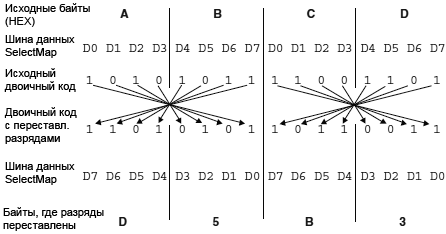

В отличие от Slave Serial режим конфигурирования SelectMAP выглядит несколько сложнее из-за порядка следования данных. Конфигурационные данные загружаются по одному байту за раз с каждым фронтом тактового сигнала CCLK, и каждый бит MSB в каждом байте подается на ножку D0, вовсе не на D7 (очень странно, почему так сделала Xilinx). Из-за этого нестандартного упорядочивания бит представление данных в файле .bin обычно неправильное. Это потому что большинство микроконтроллеров интерпретируют бит D7 (не D0) как самый значащий бит (MSB) в байте. Подключение D7 микроконтроллера на D7 шины данных FPGA SelectMAP в реальности приведет к загрузке данных «наоборот», в результате ничего работать не будет. По этой причине исходный поток данных может нуждаться в перестановке байт, при котором в каждом байте поток бит должен быть изменен на обратный. Рис. 3 показывает, как это произойдет с двумя байтами (0xABCD).

Рис. 3. Пример перекодировки байт (Byte-Swapping).

Примечание: изменен ли порядок бит в файле или нет — об этом нужно думать обычно только тогда, когда в приложении применен режим загрузки SelectMAP. Данные без изменения порядка бит должны использоваться для загрузки в режиме Slave Serial.

Если загрузка конфигурации прошла с ошибкой, вывод DONE не перейдет в состояние лог. 1 после того, как все данные были загружены. Может быть множество причин, из-за чего это может произойти. Возможные случаи и решения проблем могут быть найдены поиском по базе Xilinx Answers Database или с использованием Configuration Problem Solver на сайте support.xilinx.com.

Пример дизайна приложения основан на процессоре Motorola Dragonball MC68VZ328. Этот дизайн был использован в наладоннике Handspring Visor для конфигурирования Virtex FPGA. Для полной системы можно применить Insight Springboard Development Kit, где на плате предоставлено 32 мегабайта памяти flash, как и 256-macrocell CoolRunner™ CPLD.

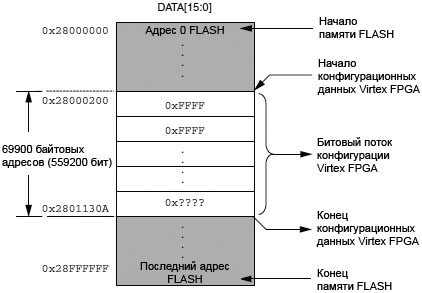

Рисунок 4 показывает карту памяти для процессора Dragonball, используемую для этой разработки. Слот расширения Handspring Visor Springboard предоставляет два региона адресного пространства с выборкой внешней микросхемы (chip select), доступных для пользователя, называемые Chip Select 0 и Chip Select 1. Память flash подключена к региону Chip Select 0, определенному как адресное пространство между 0x28000000 и 0x28FFFFFF. Микросхема CPLD подключена к региону Chip Select 1, определенному как адресное пространство между 0x29000000 и 0x29FFFFFF. Каждая ячейка памяти в адресном пространстве ссылается на 8 бит данных. Однако процессор Dragonball не поддерживает побайтную адресацию. Как следствие линия 0 шины адреса не используется. Таким образом, данные могут быть доступны в ячейках с четным адресом (т. е. 0x28000000, 0x28000002, и т. д.). Каждый доступ на чтение или запись адресует сразу 16 бит данных. Доступ к ячейкам, расположенным по нечетным адресам, запрещен.

Затененная область в нижней части карты памяти, как это показано на рисунке 4 (Internal Memory Space), представляет части памяти, используемые процессором для внутренних функций. Эта область памяти не используется в этом примере дизайна.

Рис. 4. Карта памяти микроконтроллера.

В этом примере разработки 16-битная память flash начинается с байтового адреса 0x28000000 и заканчивается адресом 0x28FFFFFF. Как показано на рис. 5, конфигурационный поток данных Virtex XCV50 состоит из 559200 бит. Поскольку каждая ячейка памяти содержит 16 бит данных, нужно всего 559200 / 16 = 34950 адресов. Первые 16 бит конфигурационных данных находятся по адресу 0x28000200, и последние 16 бит по адресу 0x2801130A (это байтовые адреса). В этом проекте адрес 0x28000200 выбран произвольно в качестве стартового, чтобы моделировать реальный пользовательский сценарий, в котором память flash может содержать также и другие системные данные.

Данные в памяти flash могут нуждаться в перестановке, в зависимости от приложения. Для этого примера разработки используются переставленные данные для конфигурации загрузки SelectMAP, но это не требуется для конфигурации Slave-Serial. Перестановка данных в байтах данных конфигурации FPGA заключается в том, что порядок бит в каждом байте меняется на обратный, как это уже описывалось в разделе «Форматирование данных и перестановка байт».

Рис. 5. Карта памяти FLASH.

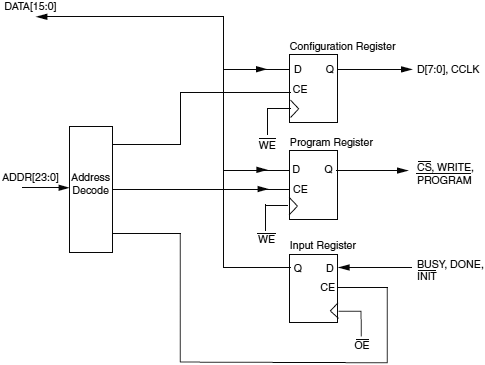

Режим конфигурирования FPGA SelectMAP позволяет микроконтроллеру быстрее сконфигурировать чип FPGA, потому что за один такт загружается не 1, а сразу 8 бит, 16 или 32 бита (в зависимости от ширины шины SelectMAP). Чтобы реализовать конфигурирование SelectMAP, этот дизайн использует комбинацию микроконтроллера, CPLD и памяти flash (см. рис. 6).

Рис. 6. Конфигурация SelectMAP.

Для хранения конфигурационных данных для FPGA используется 16-битная микросхема памяти flash. Поскольку каждый адрес flash ссылается на 16 бит данных, микроконтроллер читает каждый адрес чтобы получить 16 бит данных и передает эти данные побайтно в FPGA. Во время этого процесса микроконтроллер предоставляет для FPGA конфигурационные такты и следит за состоянием выводов DONE и BUSY. Микросхема Xilinx CoolRunner CPLD используется для формирования промежуточной логики между микроконтроллером и устройством FPGA.

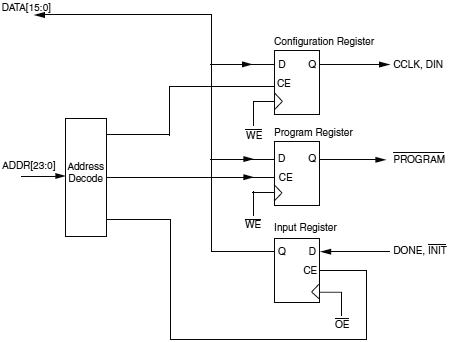

Детализированная блок-схема CPLD показана на рисунке 7.

Рис. 7. Блок-схема CPLD.

Карта регистров показана в таблице 4.

Таблица 4. Адресная карта регистров.

В этой секции обсуждается код на языке C, который позволяет микроконтроллеру выполнять следующие операции:

• Читать конфигурационные данные FPGA из памяти flash.• Генерировать такты CCLK.• Передавать побайтно данные для конфигурирования FPGA.• Проверять состояние вывода BUSY (не обязательная операция).

Примечание: разные микроконтроллеры имеют различные структуры организации ввода/вывода памяти, в зависимости от конфигурации системы. Таким образом, в то время как большинство кода C легко переносится с одной платформы на другую, пользователь все-таки должен изменить части кода, управляющие физическими операциями чтения и записи своей шины данных, чтобы они соответствовали карте памяти системы на новом микроконтроллере.

Для максимального удобства понимания и чтения весь код C, показанный в этом руководстве, выполняет доступ к шинам адреса и данных микроконтроллера унифицировано, с использованием двух простых функций: IOWrite() и IORead(). I OWrite() записывает 16-битное слово по указанному адресу; IORead() получает 16-битные данные из указанной ячейки памяти (описание синтаксиса функций см. в приложении «Описание специфичных для процессора вызовов функций ввода/вывода»).

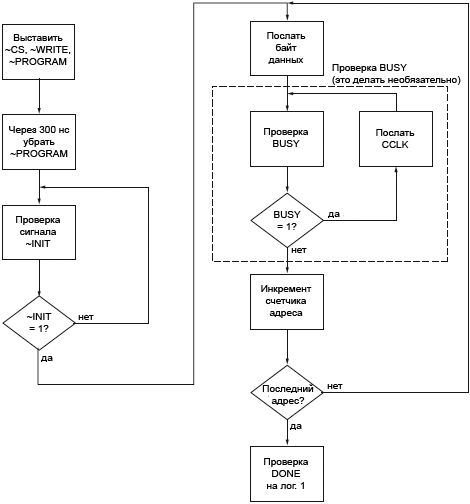

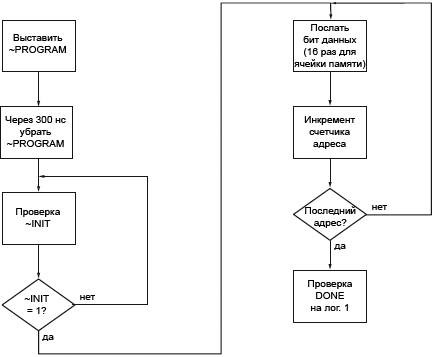

Файл исходного кода SelectMAP.c содержит 3 важные функции: SelectMAP(), SelectMAP_output() и Busy_Check(). Функция SelectMAP() вызывается, из главной функции приложения для начала конфигурации. SelectMAP() генерирует импульсы на выводе ~PROGRAM микросхемы FPGA, и проверяет состояние ~INIT. После того, как ~INIT перешел в 1, микросхема готова принять данные конфигурации, и вызывается функция SelectMAP_output(). Алгоритм работы программного обеспечения показан на рис. 8.

Рис. 8. Диаграмма работы кода конфигурирования FPGA в режиме SelectMAP.

Сначала процессор записывает Program Register, чтобы выставить вывод ~PROGRAM, что сбрасывает FPGA.

Примечание: может понадобиться цикл задержки для того, чтобы выставить вывод ~PROGRAM на минимально требуемое время (за конкретным значением времени обратитесь к даташиту на соответствующую микросхему FPGA). Если FPGA сразу готова к загрузке после включения питания, или сброс происходит по-другому, то этот цикл задержки не нужен.

После того, как выставлен бит ~PROGRAM, функция SelectMAP() проверяет CPLD Input Register, пока состояние ~INIT не окажется в лог. 1. Затем функция входит в цикл for, который проходит по всему диапазону адресов памяти flash, которые содержат конфигурационные данные для FPGA. В этом примере используется устройство FPGA XCV50, и диапазон байтовых адресов 0x28000200 . 0x2801130A. Для каждой ячейки памяти считываются 16 бит данных (адрес инкрементируется на 2), и вызывается функция SelectMAP_output() для выполнения побайтной передачи данных в FPGA.

Примечание: в функции SelectMAP_output() нужно 2 цикла для каждого байта в файле конфигурации. Один цикл нужен для перевода тактового сигнала в состояние лог. 0 и для предоставления следующего конфигурационного байта. Второй цикл нужен для перевода тактового сигнала CCLK в состояние High. Сразу после перевода вывода CCLK в состояние лог. 1 вызывается функция Busy_Check() для того, чтобы гарантировать правильный прием данных микросхемой FPGA.

Если сигнал BUSY выставлен в состояние лог. 1, то функция Busy_Check() продолжает предоставлять дополнительные циклы CCLK, пока BUSY не перейдет в лог. 0. Проверка вывода BUSY занятости FPGA является необязательной функцией, если частота записи данных не слишком высока.

Примечание: максимальная скорость конфигурирования в режиме SelectMAP различается между отдельными семействами FPGA. Для получения точных данных обратитесь к соответствующему даташиту.

После того, как все данные конфигурации загружены, цикл for заканчивается, и функция SelectMAP() проверяет CPLD Input Register на предмет выставления сигнала DONE.

В этой секции обсуждается пример разработки, который позволяет конфигурировать Virtex FPGA в режиме Slave Serial, в комбинации с микроконтроллером и микросхемой CPLD. Конфигурирование Slave Serial реализовано путем предоставления для Virtex FPGA тактового сигнала и одного сигнала данных, которые принимаются FPGA по каждому положительному перепаду (нарастающему фронту) тактового сигнала — до тех пор, пока не будет отправлен последний конфигурационный бит.

Общая схема дизайна показана на рис. 9. Для сохранения конфигурационных данных FPGA используется 16-битная память flash. Поскольку каждая ячейка памяти flash хранит 16 бит данных, микроконтроллер читает каждую ячейку, и преобразует её данные в последовательный поток бит. Этот процесс продолжается, пока не будут прочитаны и последовательно отправлены последние 16 бит конфигурационных данных. Во время этого процесса микроконтроллер также отвечает за формирование тактового сигнала конфигурирования для FPGA. Дополнительная микросхема CPLD используется для декодирования последовательного битового потока и формирования тактового импульса, и непосредственно с нее подаются сигналы конфигурирования на Virtex FPGA.

Рис. 9. Конфигурация Slave Serial.

Микросхема Xilinx CoolRunner CPLD используется в качестве связующей логики между микроконтроллером и Xilinx Virtex FPGA. В режиме конфигурирования Slave Serial микросхема CPLD отвечает за управление конфигурирующими сигналами для Virtex FPGA (~PROGRAM, CCLK и DIN). Сигналы ~INIT и DONE, приходящие от устройства Virtex, также поступают на CPLD, благодаря чему их состояние может быть прочитано микроконтроллером.

Таким образом, CoolRunner CPLD используется для установки синхронного интерфейса между микроконтроллером и Xilinx FPGA. Интерфейс доступа со стороны микроконтроллера представлен тремя регистрами: Configuration Register, Program Register и Input Register. Эти регистры хранят конфигурационные сигналы FPGA всякий раз, когда микроконтроллер выполняет чтение порта или запись в порт, что осуществляет поддержку набора сигналов, требуемых для режима Slave Serial (~PROGRAM, DIN, CCLK, ~INIT и DONE). Configuration Register и Program Register предназначены только для записи (write-only), в то время как Input Register только для чтения (read-only). Подробная блок-схема дизайна CPLD показана на рис. 10. Карта адресов регистров показана в таблице 5.

Рис. 10. Блок-схема CPLD.

Таблица 5. Адресная карта регистров.

• Читать конфигурационные данные FPGA из памяти flash.• Генерировать такты CCLK.• Передавать побитно данные для конфигурирования FPGA.

В файле исходного кода SlaveSerial.c имеются 2 функции SlaveSerial() и ShiftDataOut(), которые осуществляют конфигурирование. Чтобы начать конфигурирование, функция SlaveSerial() вызывается из функции main() приложения, и она отвечает за выдачу импульсов на выводе программирования, проверку сигнала ~INIT, и затем за вызов функции ShiftDataOut(). Алгоритм работы программного обеспечения показан на рис. 11.

Рис. 11. Диаграмма работы кода конфигурирования FPGA в режиме Slave Serial.

После того, как выставлен бит ~PROGRAM, функция SlaveSerial() проверяет CPLD Input Register, пока сигнал ~INIT не перейдет в лог. 1. Затем функция переходит в цикл for, который проходит по всему диапазону адресов flash, где записаны конфигурационные данные для FPGA. В этом примере используется устройство FPGA XCV50, и диапазон адресов flash находится между 0x28000200 и 0x2801130A. Для каждого адреса читаются 16 бит данных, и вызывается функция ShiftDataOut(), чтобы последовательно передать данные в FPGA.

Примечание: функция ShiftDataOut() использует 2 цикла для каждого конфигурационного бита. Один цикл нужен чтобы перевести сигнал CCLK в состояние лог. 0, и выставить следующий конфигурационный бит. Второй цикл нужен для перевода CCLK в состояние лог. 1. После того, как конфигурационные данные загружены, цикл завершается, и функция SlaveSerial() проверяет CPLD Input Register на предмет выставления сигнала DONE.

При использовании функции IOWrite() ей в качестве параметров должны быть переданы адрес и данные. В примере дизайна, который здесь приведен, адреса регистров Configuration, Program и Input находятся соответственно в ячейках 0x29000000, 0x29000002 и 0x29000004. Поэтому функция используется только для записи по этим трем адресам.

Таблица 6. Примеры использования IOWrite().

Диаграммы времени цикла записи микроконтроллера показаны на рисунке 12.

Рис. 12. Диаграммы сигналов процесса записи.

Для использования функции IORead в качестве параметра нужно передать адрес. По этому адресу будет прочитана и возвращена 16-битная величина. В этом примере дизайна данные читаются по диапазону адресов 0x28000200 . 0x2801130A (область памяти, где хранятся конфигурационные данные FPGA), а также по адресу 0x29000004 (адрес доступа к Input Register).

Таблица 7. Примеры использования IORead().

Диаграммы времени цикла чтения микроконтроллера показаны на рисунке 13.

Рис. 13. Диаграммы сигналов процесса чтения.

BitGen утилита командной строки (входит в пакет Xilinx ISE Design Tools), которая предназначена для создания файла прошивки микросхемы FPGA (конфигурационный файл FPGA).

CPLD Complex Programmable Logic Device, программируемая логическая интегральная схема (ПЛИС) в диапазоне сложности между микросхемами PAL (Programmable Array Logic) и FPGA (Field-Programmable Gate Array), сочетающая их архитектурные решения (из Википедии). Говоря по-русски, не очень сложная микросхема программируемой логики, в которой логика уже загружена в момент программирования, и она сохраняется между выключениями питания.

FPGA Field-Programmable Gate Array — полупроводниковое устройство (микросхема), которое может быть сконфигурировано производителем или разработчиком после изготовления; отсюда название: «программируемая пользователем». П ПВМ программируются путём изменения логики работы принципиальной схемы, например, с помощью исходного кода на языке проектирования (типа VHDL), на котором можно описать эту логику работы микросхемы. П ПВМ является одной из архитектурных разновидностей программируемых логических интегральных схем (ПЛИС) (из Википедии). Говоря по-русски, это довольно сложная программируемая микросхема логики, логическая схема работы которой обычно загружается в момент включения питания из какой-то внешней памяти или под управлением микроконтроллера.

GPIO General Purpose Input/Output, порты ввода/вывода общего назначения. Ножки микроконтроллера, которыми он может управлять (и состояние которых он может считывать) с помощью своего программного обеспечения.

LSB Least Significant Bit, самый младший значащий бит.

MSB Most Significant Bit, самый старший значащий бит.

Platform Flash PROM микросхема памяти, специально предназначенная для хранения конфигурационных данных FPGA Xilinx.

PROM Programmable Read-Only Memory, класс полупроводниковых запоминающих устройств, постоянная память с пережигаемыми перемычками (из Википедии). На самом деле вовсе не обязательно, что в этой памяти действительно есть какие-то перемычки. Имеется в виду, что память не перепрограммируется во время своего использования, и хранящиеся в ней данные не предназначены для изменения.

PROMGen специальная утилита Xilinx, предназначенная для переформатирования конфигурационного файла (файл с расширением BIT, который сгенерирован утилитой BitGen) в формат PROM (файл для заливки в микросхему PROM, из которой будет загружаться FPGA).

SelectMAP режим программирования FPGA под управлением микроконтроллера, при котором конфигурационные данные подаются параллельно порциями по 8 бит (или по 16, или по 32 бита, в зависимости от ширины шины данных SelectMAP). Этот режим также называют Slave Parallel.

Slave Serial то же самое, что и SelectMAP, но здесь конфигурационные данные подаются по 1 биту.

1. Using a Microprocessor to Configure Xilinx FPGAs via Slave Serial or SelectMAP Mode, XAPP502 (v1.6.1) August 24, 2009.2. Configuration for Spartan-3A/3E FPGAs site:xilinx.com.3. I SE® software manuals site:xilinx.com.4. 140922xilinx-FPGA-prog-MCU.zip — документация, примеры кода микроконтроллера.5. Gameduino: сборка, компиляция исходного кода Verilog, тестирование.

Макро Групп

www.macrogroup.ru • Контактная информация